Description

TrackCore-F is a methodology and collection of techniques to deploy Machine Learning (ML) models involved in ML-assisted particle track reconstruction algorithms on FPGAs. With TrackCore-F, the focus is the deployment of the ML model element, specifically aiming at the Transformer architecture. As such, FPGA-accelerated inference can boost tracing performance by reducing the computation latency. The small form factor and low power requirements of FPGAs enables on-site installation and paves the way for potential online tracking, as opposed to current post-mortem approaches. Currently, TrackCore-F operates to convert pre-trained models taken from the project TrackFormers as input. However, the techniques to convert and evaluate common Transformer blocks, e.g., encoder layers, are generally applicable.

Development workflow

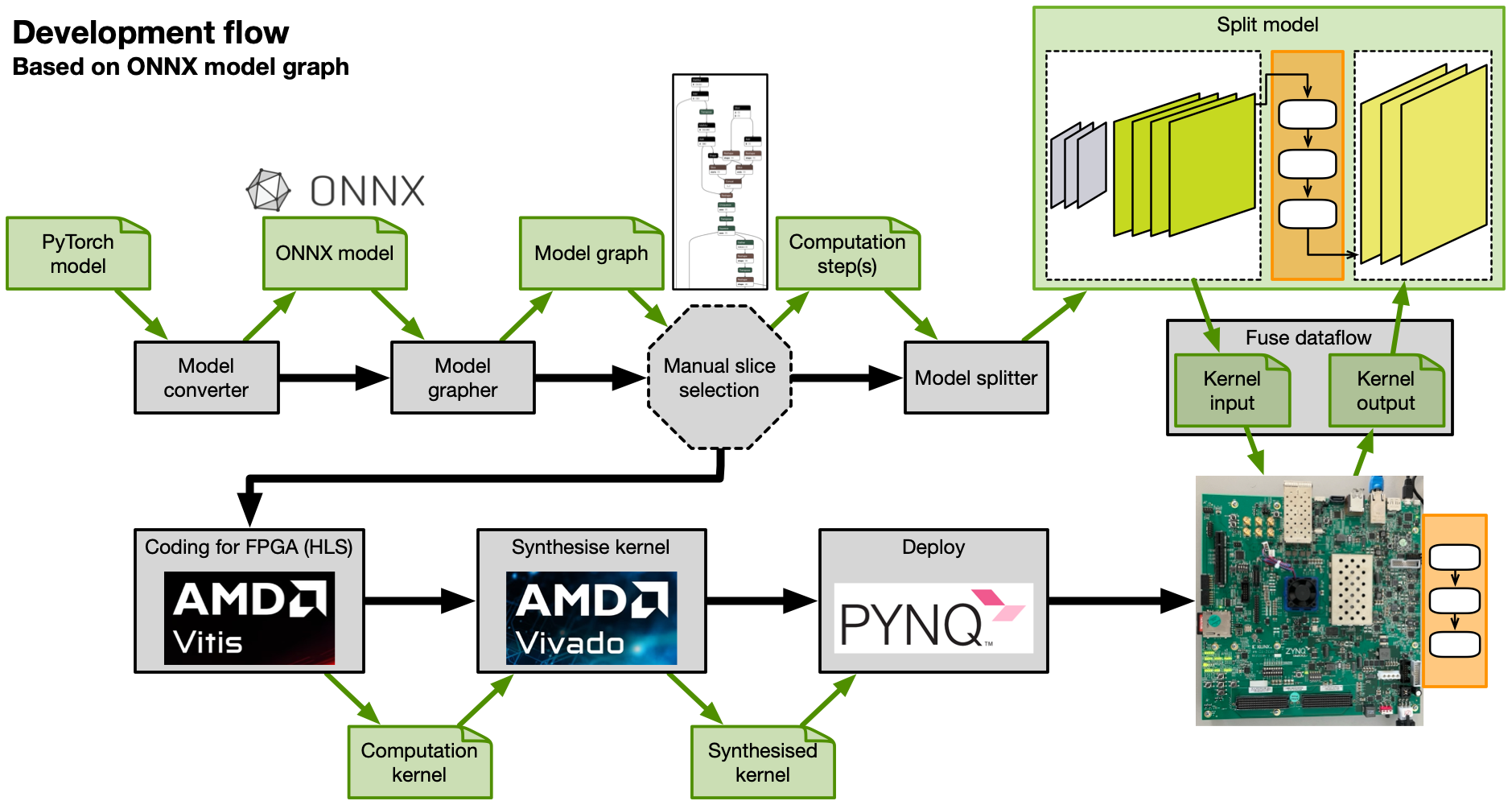

Achieving deployable syntheses for pre-trained ML models will require going through multiple steps, performing analysis, and involves a variety of tooling. We consider models expressed in PyTorch model format as the starting point. FPGA deployment will also demand considerations and deciding on a full or partial acceleration. Either strategy can be motivated based on different factors, some being use-case dependent. The complete development workflow for a partial acceleration is depicted in Figure 1.

PyTorch model format does not provide granular visibility and individual access to a model's internal computational steps. By converting the model to Open Neural Network Exchange (ONNX) format, a detailed model graph can be extracted. Partitioning the model into separate slices is done in Python. This is followed by coding a computation kernel in HLS, synthesising this kernel, and deployment using AMD Vitis HLS, AMD Vivado HLS, and PYNQ, respectively. Further details can be found in our EuCAIFCon 2025 proceedings paper [1].

Feature set

In its current form, TrackCore-F is more of an experimental workflow than a reusable tool. The below listing covers targeted functionality for a reusable version. Current availability is indicated using status markers.

Orange: Limited selection

Red: Under development

| Category | Feature | Status |

|---|---|---|

| TBA | TBA |

|

| TBA | TBA |

|

Code repository

TBA ...

Publications

Abstract

The Transformer Machine Learning (ML) architecture has been gaining considerable momentum in recent years. In particular, computational High-Energy Physics tasks such as jet tagging and particle track reconstruction (tracking), have either achieved proper solutions, or reached considerable milestones using Transformers. On the other hand, the use of specialised hardware accelerators, especially FPGAs, is an effective method to achieve online, or pseudo-online latencies. The development and integration of Transformer-based ML to FPGAs is still ongoing and the support from current tools is very limited to non-existent. Additionally, FPGA resources present a significant constraint. Considering the model size alone, while smaller models can be deployed directly, larger models are to be partitioned in a meaningful and ideally, automated way. We aim to develop methodologies and tools for monolithic, or partitioned Transformer synthesis, specifically targeting inference. Our primary use-case involves two machine learning model designs for tracking, derived from the TrackFormers project. We elaborate our development approach, present preliminary results, and provide comparisons.

Abstract

With the rapid and continuous growth in the incorporation of machine learning models based on the Transformer architecture, capable deployment is in high demand. In this context, capable deployment refers to operational performance aspects, e.g., throughput and latency, as well as efficiency aspects, e.g., energy consumption. When it comes to the task of inference using such models, purpose-built hardware accelerators provide a lucrative alternative to common deployment choices, such as Central Processing Units (CPUs) and Graphics Processing Units (GPUs). Field Programmable Gate Array (FPGA) platforms category is an example of such alternative accelerators, promising implementation flexibility, energy-efficiency, improved latency and suitability for on-site deployment. We investigate the most recent advances, trends, and design choices for Transformer inference on FPGA platforms. We perform a systematic literature review, extracting and delving into preferred techniques for implementation and optimisation. This study and the provided taxonomy of topics could act as a guide for researchers from the academia and industry alike.